Samsung said Thursday it is on track to start high-volume production using its 3nm-class gate all-around early (3GAE) manufacturing process this quarter (i.e. within weeks). coming). The announcement not only marks the industry’s first 3nm class fabrication technology, but also the first node to use all-around-the-gate field-effect transistors (GAAFET).

“Enhancing technology leadership via the world’s first mass production of the GAA 3-nano process,” a statement [PDF] by Samsung reads.

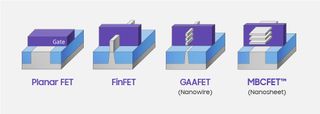

Samsung Foundry’s 3GAE process technology is the company’s first process to use GAA transistors, which Samsung officially calls Multi-Bridge Channel Field Effect Transistors (MBCFETs).

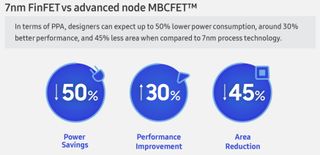

Samsung officially introduced its 3GAE and 3GAP nodes about three years ago. When the company described its 256MB GAAFET SRAM chip produced using its 3GAE technology, it made a number of claims. Samsung said the process would deliver a 30% performance boost, 50% lower power consumption, and up to 80% higher transistor density (including a mix of logic and SRAM transistors). It remains to be seen how the actual combination of performance and power consumption will play out for Samsung.

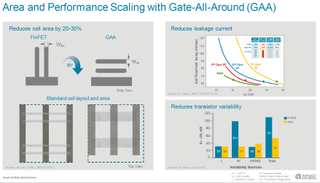

In theory, GAAFETs have a number of advantages over currently used FinFETs. In GAA transistors, the channels are horizontal and are surrounded by gates. GAA channels are formed by epitaxy and selective material removal, allowing designers to fine-tune them by adjusting the channel width of the transistor. High performance is achieved through wider channels, low power through narrower channels. Such precision dramatically reduces transistor leakage current (i.e. reduces power consumption) as well as variability in transistor performance (assuming everything is working fine), which means a turnaround time faster, time to market and improved yields. Additionally, GAAFETs promise to reduce cell surface area by 20-30%, according to a recent presentation from Applied Materials.

Speaking of Applied, he recently described high-vacuum Integrated Materials Solution (IMS) systems intended to address a major challenge in GAA transistor fabrication: the need to deposit multilayer gate oxide and metal gate stacks. around the channels in the small space available. . Applied Materials’ first new IMS tool can deposit 1.5 Angstrom thinner gate oxide using integrated atomic layer deposition (ALD), thermal, plasma processing and metrology steps. The IMS metal gate incorporates dipole engineering and a variety of ALD stages.

Samsung’s 3GAE, being an “early” 3nm class manufacturing technology, 3GAE will primarily be used by Samsung LSI (the chip development arm of Samsung) and perhaps one or two of SF’s other alpha customers. Bearing in mind that Samsung’s LSI and other early SF customers tend to build chips in very high volumes, expect 3GAE technology to be used quite widely, assuming yields and the performance of these products meets expectations.

Transitioning to an entirely new transistor structure is usually a risk because it involves an entirely new manufacturing process as well as entirely new tools. Other challenges are new placement methodologies, floor plan rules, and routing rules that are introduced by all new nodes and handled by new Electronic Design Automation (EDA) software. Finally, chip designers have to develop brand new IP, which is expensive.

More Stories

Delay in mass production of new Intel products is a boon for AMD, share of AMD x86 server processors expected to exceed 22% in 2023, according to TrendForce

Quantum industry milestone brings mass production of quantum chips closer

NEO Battery Materials provides updates on installation of additional equipment for mass production optimization and final stages of commercial plant design for construction